# **CMOS 8–Bit Microprocessor**

# TMP90C051F

## 1. Overview and Features

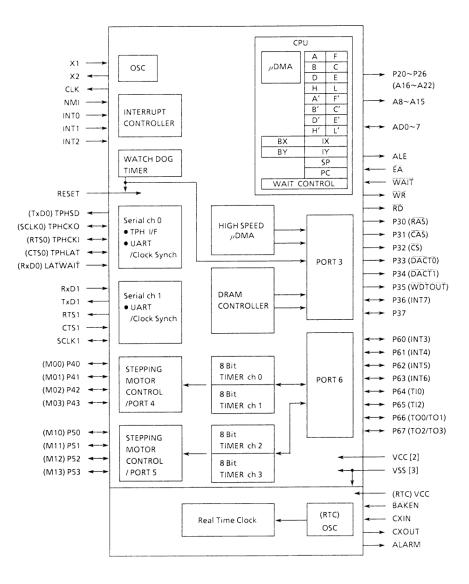

The TMP90C051F is a high-speed 8-bit CMOS microprocessor with advanced functions and was developed for application in various types of device control.

The TMP90C051F is a single-chip, 8-bit CMOS microprocessor that integrates peripheral functions such as DMA, DRAM controller, serial interface, timer/event counter and real time clock with an 8-bit CPU (TLCS90) core. Memory area can also be extended up to 8M bytes depending on the MMU.

The TMP90C051F features are as follows.

- Highly efficient instruction group Number of basic instructions: 167 Multiplication and division instructions, 16-bit arithmetic operation instructions and bit operation instructions.

- (2) Minimum instruction execution times: 250ns (at 16.0MHz)

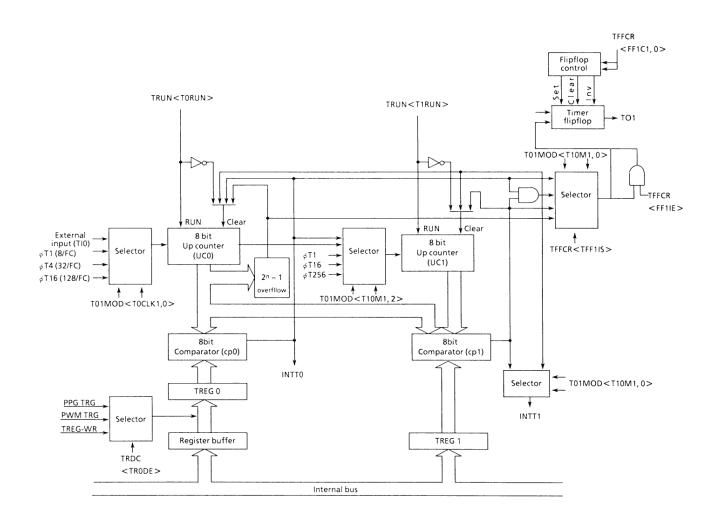

- (3) Memory extension capability Address space: 8M byte (max)

- (4) DMA (2 channels)Maximum transfer speed: 2-byte transfer;0.88M byte/sec (at 16.0MHz)

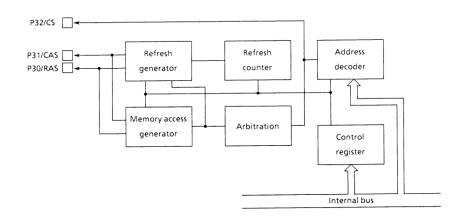

- (5) DRAM controller

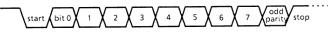

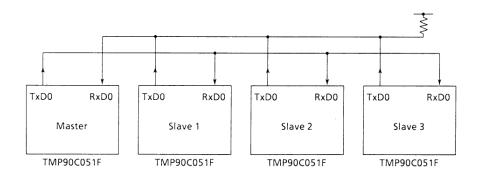

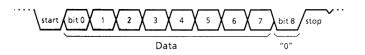

- (6) General-purpose serial interface (2 channels) UART (transmit/receive)

- I/O interface mode (transmit/receive)

- (7) Thermal printer head (transmit)

- (8) 8-bit timer/event counter (4 channels)

- (9) Real time clock: Clock and calendar functions/battery backup capability.

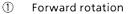

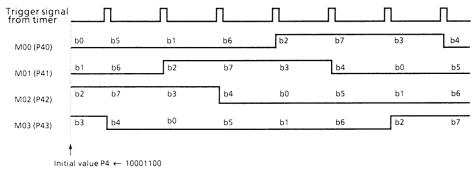

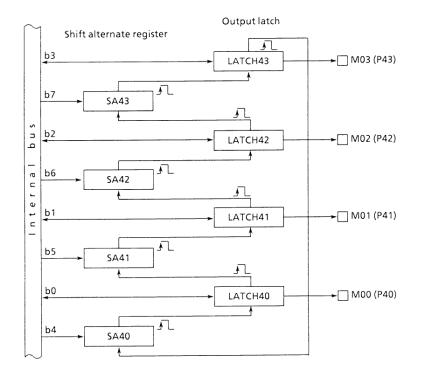

- (10) Stepping motor control pattern generation ports (2 channels)

- (11) Input/output port (31-pin)

- (12) Interrupt functions:11 internal, 9 external.

- Micro DMA function

Maximum transfer speed: 0.34M byte/s (at 16.0MHz)

- (14) Watchdog timer function

- (15) Standby function (3 halt modes)

The information contained here is subject to change without notice.

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments (office equipment, communication equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

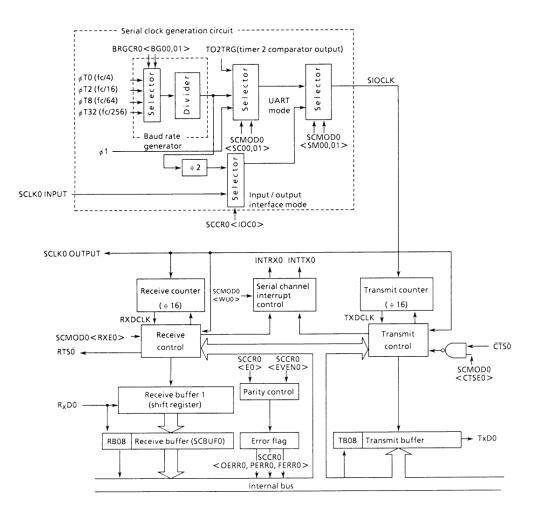

Figure 1. TMP90C051F Block Diagram

# 2. Pin Layout and Functions

This section shows the TMP90C051F pin layout diagram, and describes the input/output pin names and functions.

# 2.1 Pin Layout Diagram

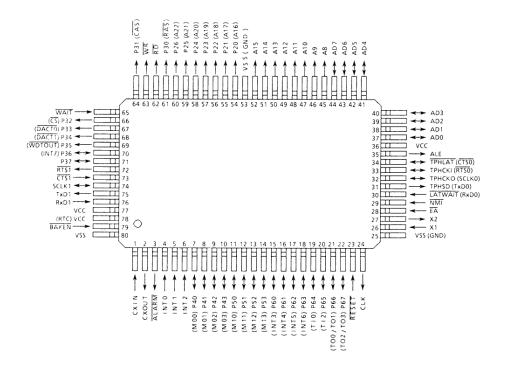

Figure 2.1 shows the TMP90C051F pin layout.

Figure 2.1. Pin Layout Diagram (80-pin Flat Package) [TOP VIEW]

# 2.2 Pin Names and Functions

Table 2.2 Shows the input/output pin names and functions.

| Pin Name                 | Number of pins<br>(pin no.) | Input/output or tristate | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------|-----------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

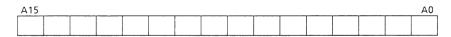

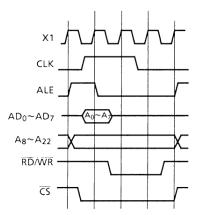

| AD0 ~ AD7                | 8<br>(37 ~ 44)              | Input/output or tristate | Lower address/data bus: Used as both the lower 8-bit address bus (output) and data bus (bi-directional).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A8 ~ A15                 | 8<br>(45 ~ 52)              | Output                   | The upper 8-bit address bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

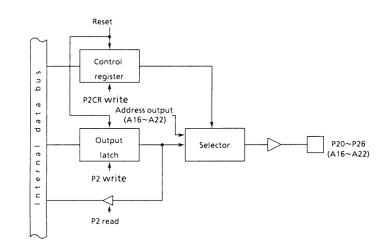

|                          |                             | Output                   | Port 2: A 7-bit output port. Outputs "0" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

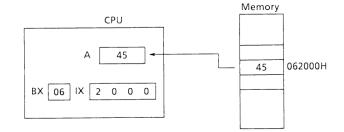

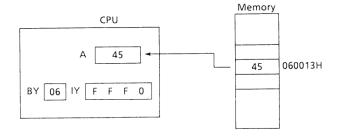

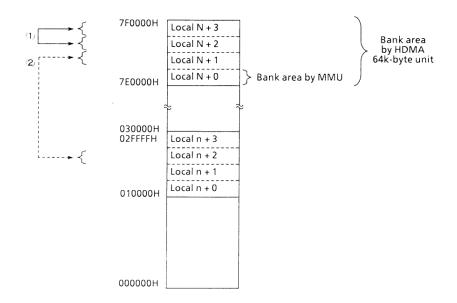

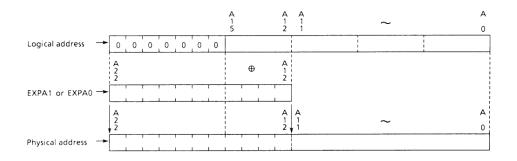

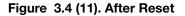

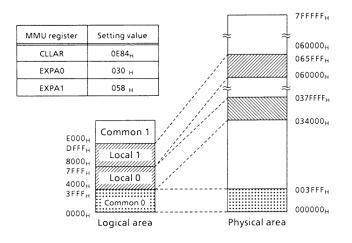

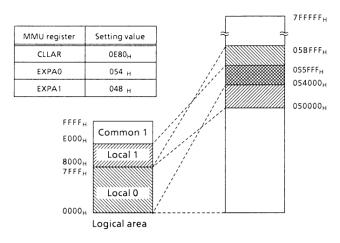

| P20 ~ P26<br>(A16 ~ A22) | 7<br>(54 ~ 60)              | Output                   | Address bus: The extension (upper) address bus. Outputs "0" after reset; there-<br>fore, the TMP90C051F address area is 0 - 64K bytes until a value other than<br>000H is written to EXPA0 and EXPA1 of the MMU register group after a reset;<br>therefore, A16 - A22 output zeros (0).<br>When a logical address indicates within the local area (local 0 or local 1) range<br>when the MMU is started, the physical addresses generated by the MMU are<br>outputs to A16 - A22.<br>Zeros (0) are output to A16 - A22 when a logical address indicates within the common<br>area (common 0 or common 1) range.<br>When an indirect extension address area is accessed using the CPU index regis-<br>ter the address value loaded to the BX or BY register is output to A16 - A22.<br>When data are transferred using high-speed micro DMA, the address value loaded to<br>the DMA bank register is output to A16 - A22. |

| RD                       | 1<br>(62)                   | Output                   | Read: The strobe signal output used to read data from external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WR                       | 1<br>(63)                   | Output                   | Write: The strobe signal output used to write data to external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WAIT                     | 1<br>(65)                   | Input                    | Wait: An input pin used to connect memory with slow access time and peripheral LSIs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NMI                      | 1<br>(29)                   | Input                    | Non-maskable interrupt request pin:<br>The input pin used to generate interrupt requests on the fall edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

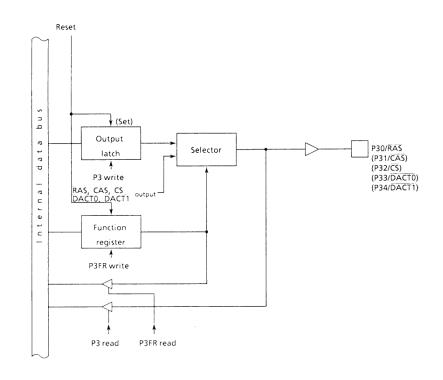

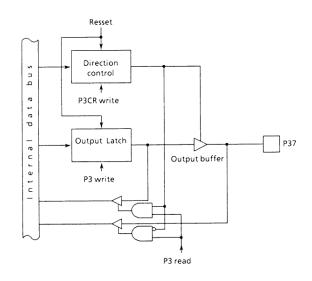

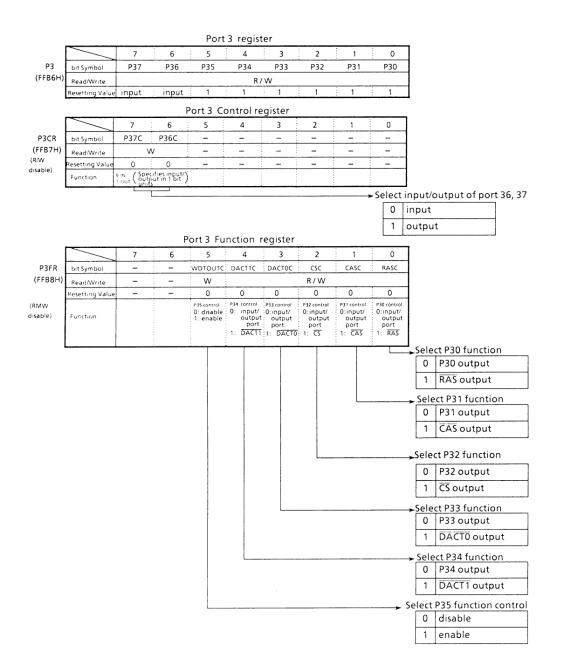

| P30                      | (1)                         | Output                   | Port 30: A 1-bit output port. Outputs "1" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

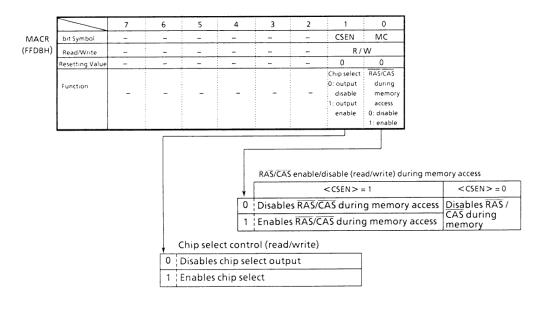

| (RAS)                    | (61)                        | υιίμαι                   | RAS: Outputs the RAS timing required for refreshing the DRAM of CAS before RAS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P31                      | 1                           | lanut                    | Port 31: A 1-bit output port. Outputs "1" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (CAS)                    | (64)                        | Input                    | CAS: Outputs the CAS timing required for refreshing the DRAM of CAS before RAS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                          |                             |                          | Port 32: A 1-bit output port. Outputs "1" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

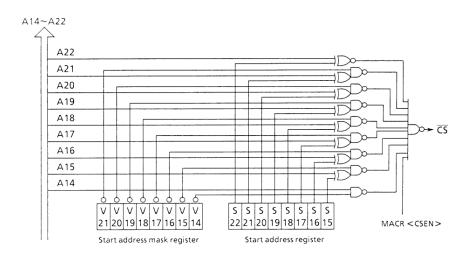

| P <u>32</u><br>(CS)      | 1<br>(66)                   | Output                   | Chip select: The external memory chip select output pin. When a start address and area size are loaded to the control register in the dynamic RAM controller, "0" is output from the CS pin whenever the TMP90C051F accesses that address range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Doo                      | -1                          |                          | Port 33: A 1-bit output port. Outputs "1" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (DACT0)                  | 1<br>(67)                   | Output                   | DMA active 0: Outputs zeros (0) while data are being transferred via high-speed micro DMA channel 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Table 2.2 Pin Names and Functions (1/3)

| Pin Name         | Number of pins<br>(pin no.) | Input/outpu t or tristate | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-----------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                             |                           | Port 34: A 1-bit output port. Outputs "1" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P34<br>(DACT1)   | 1<br>(68)                   | Output                    | DMA active 1: Outputs zeros (0) while data are being transferred via high-speed micro DMA channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

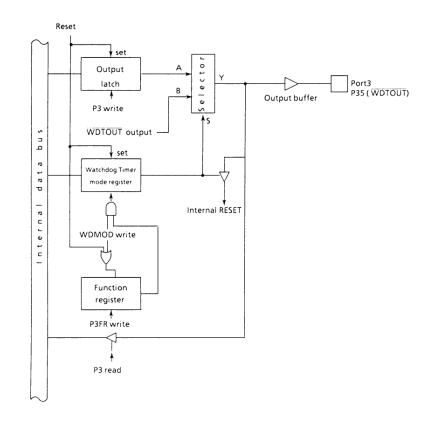

| P35              | 1                           |                           | Port 35: A 1-bit output port. Outputs "WDTOUT = 1" after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (WDTOUT)         | (69)                        | Output                    | Watchdog timer output: used as the $\overline{\text{WDTOUT}}$ output pin when watchdog timer mode register, D1 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

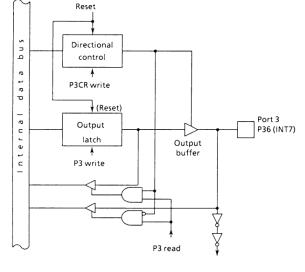

| P36              | 1                           | Input/Output              | Port 36: A 1-bit output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| (INT7)           | (70)                        | Input                     | Interrupt request pin 7: The input pin for generating interrupt requests at rise edges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P37              | 1<br>(71)                   | Input/output              | Port 37: A 1-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

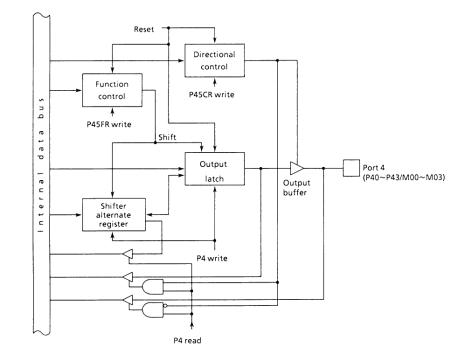

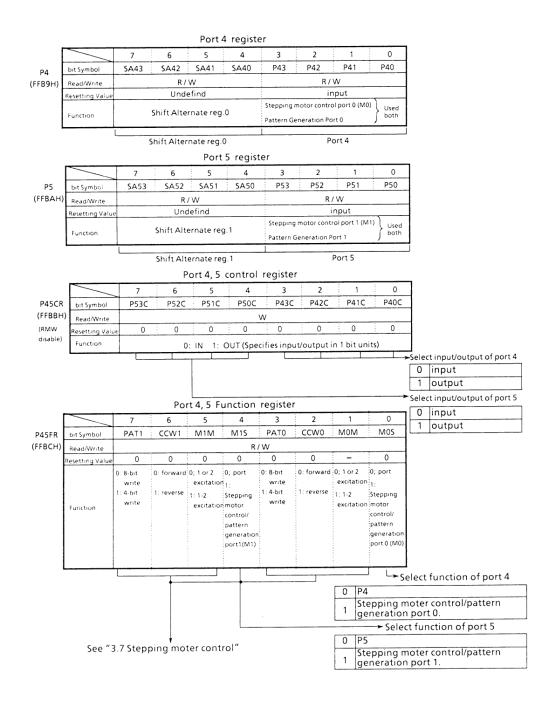

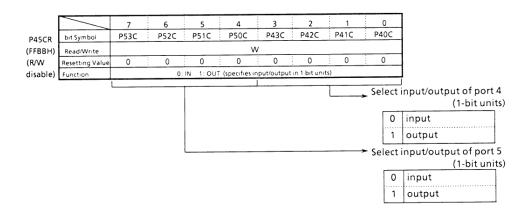

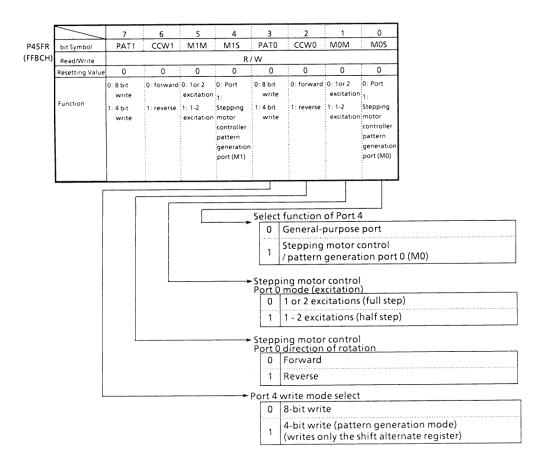

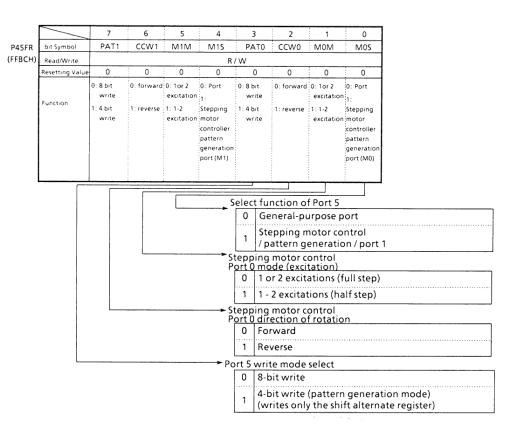

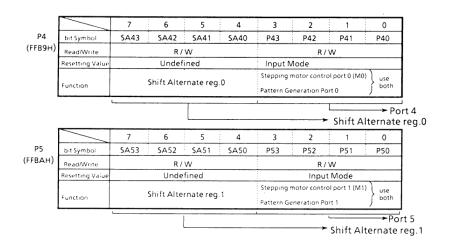

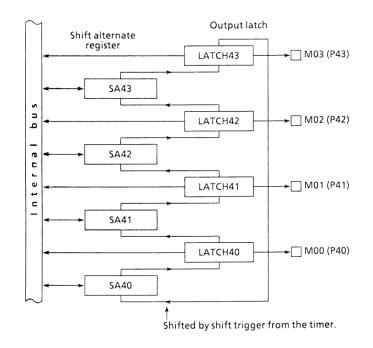

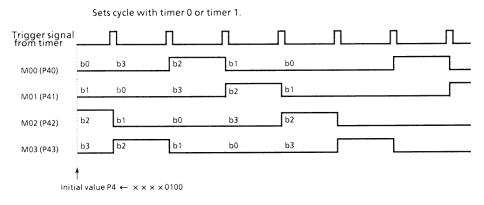

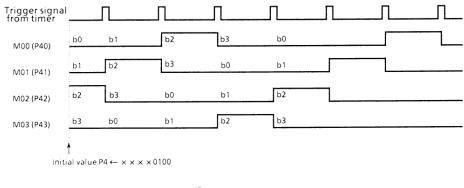

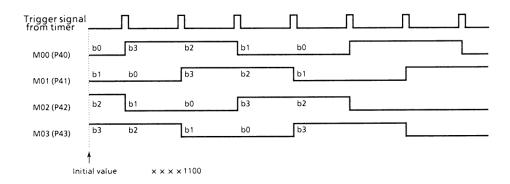

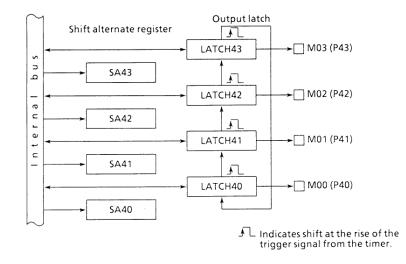

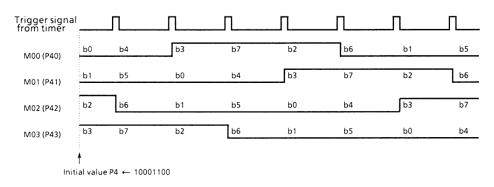

| P40 ~ P43        | 4                           | Input/output              | Port 40 - 43: A 4-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 140~140          | (7 ~ 10)                    | Output                    | Stepping motor control port 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

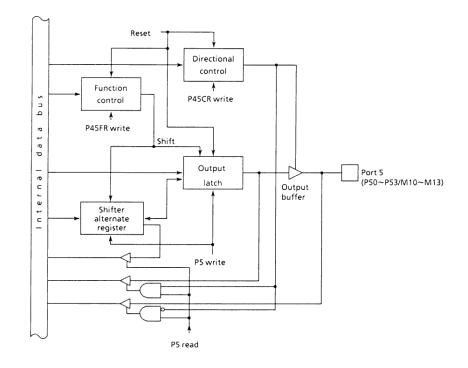

| P50 ~ P53        | 4                           | Input/output              | Port 50 - 53: A 4-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (M10<br>~ M03)   | (11 ~ 14)                   | Output                    | Stepping motor control port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

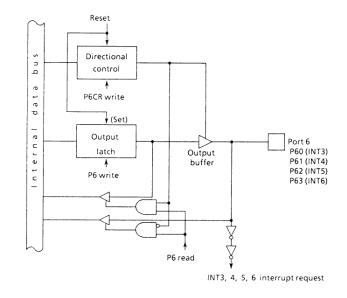

| P60 ~ P63        | 4                           | Input/output              | Port 60 ~ 63: A 4-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (INT3<br>~ INT6) | (15 ~ 18)                   | Input                     | Interrupt request pins 3-6: Input pins for generating interrupt requests at rise edges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

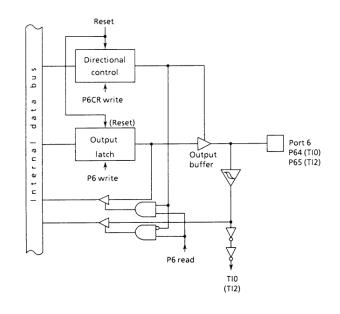

| P64              | 1                           | Input/output              | Port 64: A 1-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (TIO)            | (19)                        | Input                     | Timer input 0: The timer 0 clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P65              | 1                           | Input/output              | Port 65: A 1-bit input/output port. Functions as an input port after reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (Tl2)            | (20)                        | Input                     | Timer input 2: The timer 2 clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

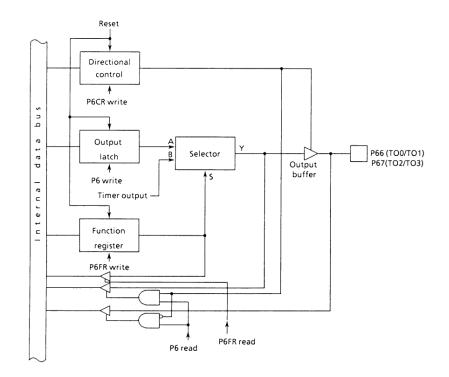

| P66              | 1                           | Input/output              | Port 66: A 1-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (T00/T01)        | (22)                        | Output                    | Timer output 0/1: The timer 0 or timer 1 output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P67              | 1                           | Input/output              | Port 67: A 1-bit input/output port. Functions as an input port after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (T02/T03)        | (23)                        | Output                    | Timer output 2/3: The timer 2 or timer 3 output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

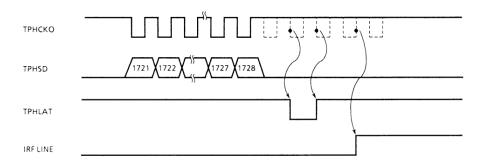

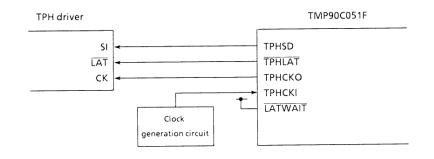

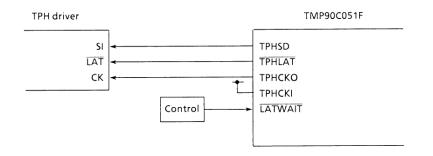

| LATWAIT<br>RxD0  | 1 (30)                      | Input                     | Set serial channel 0 to the TPH mode after reset. The wait control input pin used to cause TPHLAT output to wait.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                  | (30)                        |                           | Used as the receive data input pin when serial channel 0 is set to the Normal mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

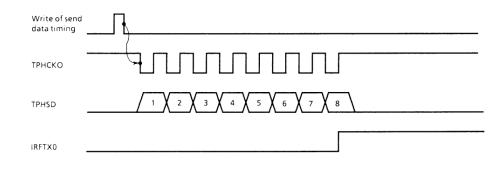

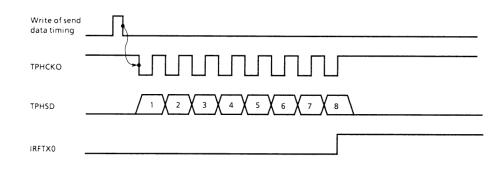

| TPHSD            | 1                           | Output                    | Serial channel 0 enters the TPH mode and outputs "0" after a reset. The TPHSD pin is used to output transmit data to TPH.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (TxD0)           | (31)                        | output                    | When set to the Normal mode, serial channel 0 functions as the transmit data output pin TXD0 output immediately after mode is set.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

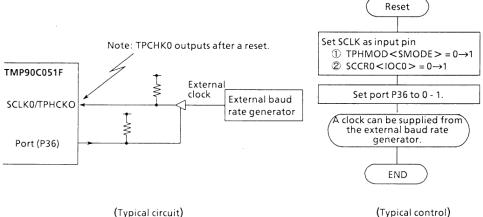

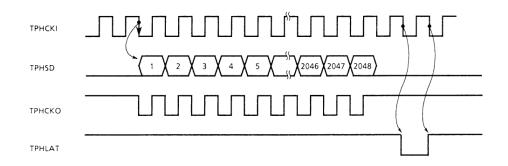

| ТРНСКО           | 1                           | Output                    | After a reset, serial channel 0 enters the TPH mode and outputs "1". The TPHCK0 pin is used to output the transmit clock to TPH.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

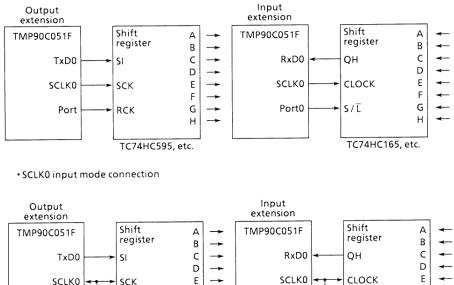

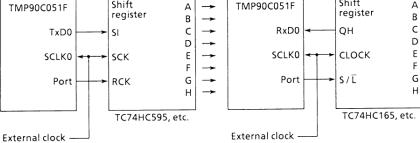

| (SCLKO)          | (32)                        | Input/output              | When set to the Normal mode by the TPH control register, serial channel 0 operates in the UART or I/O interface mode.<br>The control register of serial channel 0 determines whether the UART or I/O interface mode is used.<br>In the I/O interface mode, either the external clock from SCLK0 or the transmit/receive clock from the internal baud rate generator is output. Note: When operating with external clock inout in the I/O interface mode SCLK0 is output after a reset; therefore, use an open drain circuit to connect the external clock to the SCLK0 pin. |

| Table 2.2. Pin Names an | nd Functions (2/3) |

|-------------------------|--------------------|

|-------------------------|--------------------|

| Pin Name              | No. of pins<br>(pin. no.) | Input/output or tristate | Function                                                                                                                                                                                                                                                                       |

|-----------------------|---------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TPHCKI                | 1                         | Input                    | Serial channel 0 enters the TPH mode after a reset and functions to input the transmit clock to TPH.                                                                                                                                                                           |

| (RTSO)                | (33)                      | Output                   | Serial channel 0 is the TPH control register and operates as the RTS output pin when set to the Normal mode.                                                                                                                                                                   |

| TPHLAT                | 1                         | Output                   | After a reset, serial channel 0 enters the TPH mode and the functions as the latch signal pin for outputs to TPH.                                                                                                                                                              |

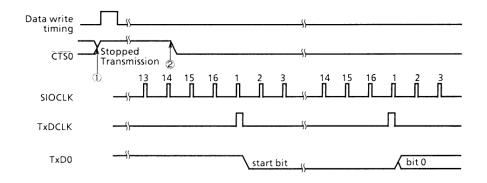

| (CTSO)                | (34)                      | Input                    | When set to the Normal mode by the TPH control register, serial channel 0 operates as the CTS0 input pin.<br>Consequently, since the CTS0 pin outputs after a reset, use an open drain circuit to connect the CTS0 pin to CTS0 when serial channel 0 is used in the UART mode. |

| RTS1                  | 1<br>(72)                 | Output                   | The serial channel 1 RTS1 output pin.                                                                                                                                                                                                                                          |

| CTS1                  | 1<br>(73)                 | Input                    | The serial channel 1 CTS1 input pin.                                                                                                                                                                                                                                           |

| SCLK1                 | 1<br>(74)                 | Input/output             | Functions as the serial channel 1 transceive clock input or output pin. SCLK1 functions as an input pin after a reset.                                                                                                                                                         |

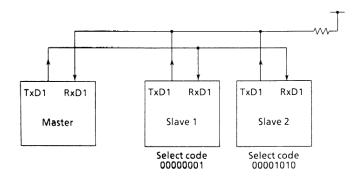

| TxD1                  | 1<br>(75)                 | Output                   | The serial channel 1 transmit data output pin.                                                                                                                                                                                                                                 |

| RxD1                  | 1<br>(76)                 | Input                    | The serial channel 1 receive data input pin.                                                                                                                                                                                                                                   |

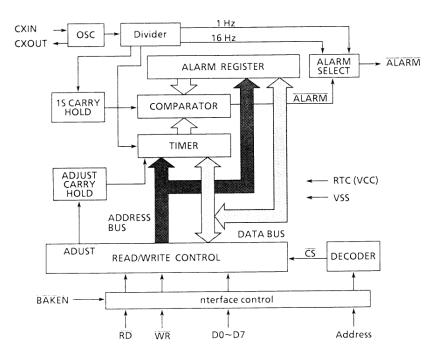

| CXIN/CXOUT            | 2<br>(1/2)                | Input/output             | Used to connect the crystal oscillator for the real time clock. A 32.768kHz crystal oscillator is usually connected.                                                                                                                                                           |

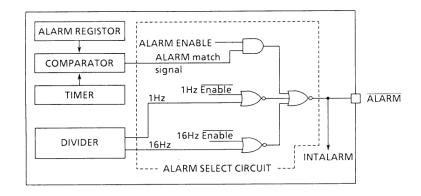

| ALARM                 | 1<br>(3)                  | Output                   | Alarm: The output pin for alarms from the real time clock. Comparator output and either the 16Hz or 1Hz signal generated by the divider can be output to the ALARM pin using the alarm select circuit inside the real time clock.                                              |

| INTO ~ INT2           | 3<br>(4~6)                | Input                    | Interrupt request pins 0 - 2: The input pin used to generate interrupt requests at rise edges.<br>INTO is an input pin with a Schmitt circuit.                                                                                                                                 |

| ALE                   | 1<br>(35)                 | Output                   | Address latch enable signal: ADO - AD7 addresses are latched on the fall of this signal.<br>Connected to external memory.                                                                                                                                                      |

| ĒĀ                    | 1<br>(28)                 | Input                    | Connect to GND.                                                                                                                                                                                                                                                                |

| CLK                   | 1<br>(24)                 | Output                   | Clock output: Output a clock equal to the oscillation frequency divided by 4. Pulled up during resets.                                                                                                                                                                         |

| RESET                 | 1<br>(23)                 | Input                    | Reset: The reset input pin used to initialize the TMP90C051F. (Built-in pull up register)                                                                                                                                                                                      |

| X1/X2                 | 2<br>(26/77)              | Input/Output             | Used to connect the crystal oscillator that generates the TMP90C051 internal system clock.                                                                                                                                                                                     |

| V <sub>CC</sub>       | 2<br>(36/77)              | -                        | Main power supply pin (+5V)                                                                                                                                                                                                                                                    |

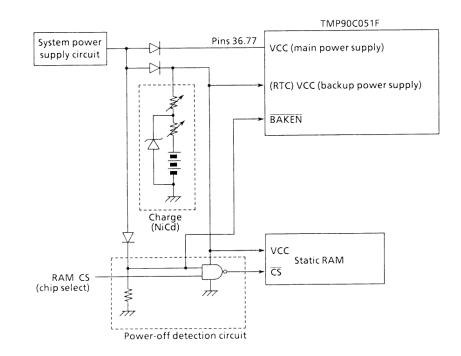

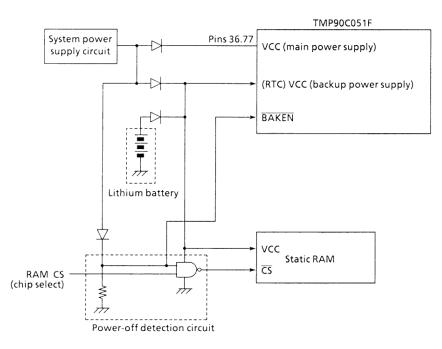

| BAKEN                 | 1<br>(79)                 | Input                    | Backup enable: set BUKEN = 1 when the TMP90C051F main power supply Vcc (pins 36/<br>77) is +5V.<br>Set to BUKRN = 0 to provide battery backup for the real time clock when the main power<br>supply Vcc (pins 36/77) is off.                                                   |

| V <sub>CC (RTC)</sub> | 1<br>(78)                 | -                        | The real time clock backup power supply pin. Arrange so that the same power is supplied to Vcc (RTC) as to Vcc (pins 36/77) when power is being supplied to Vcc (pins 36/77). To provide battery backup for only the ral time clock, supply + 5V - 2V to Vcc (RTC).            |

| V <sub>SS</sub> (GND) | 3<br>(25/53/80)           | -                        | GND pin (0V)                                                                                                                                                                                                                                                                   |

# Table 2.2 Pin Names and Functions (3/3)

# 3. Operation

This section explains the functions and basic operations of the TMP90C051F by block.

# 3.1 CPU

The TMP90C051F includes a high performance 8 bit CPU. For the function of the CPU, see the book TLCS 90 Series CPU Core Architecture. This chapter explains exclusively the functions of the CPU of TMP90C051F which are not described in the the book.

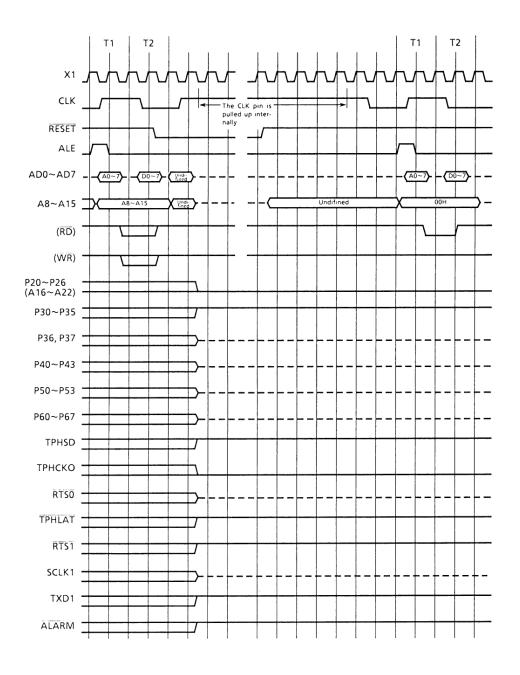

## 3.1.1 Reset

Figure 3.1 (1) shows the basic timing for the reset operation. To reset the TMP90C051F, it is necessary to maintain the RESET input at "0" for at least 10 system clocks (10 states: 2 microseconds with a 10MHz system clock) with the power supply voltage within the operating range and stable internal oscillator operation.

When a reset is received, the address data bus (AD0 - AD7), address bus (A8 - A15), P36, P37, port 4 port 5 and port 6 are all set to input port status (high impedance). Dedicated output port 2 (A16 - A22) ALE is set to "0"; P30 - P35, RD, WR and CLK are set to "1". The other dedicated output ports are all set to "0" and the dedicated input ports retain their current status.

The CPU registers and external memory are not changed; however, the program counter PC, interrupt enable/disable flag IFF, bank registers BX and BY are cleared to "0". The A register is indeterminate.

When the reset is released, the instruction starts from address 0000H.

Figure 3.1 (1). Reset Timing

# 3.1.2 EXF (Exchange Flag)

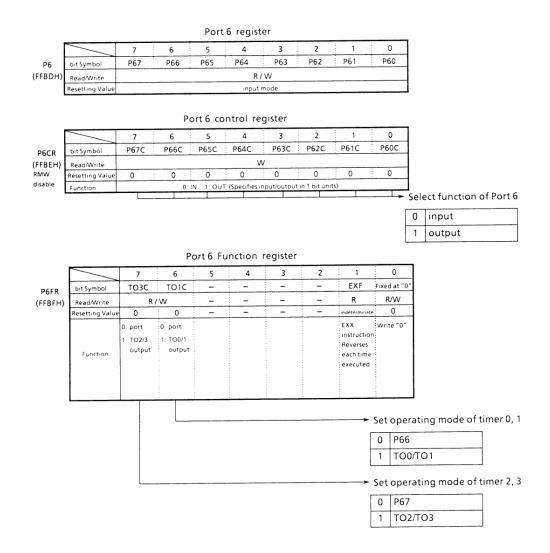

For TMP90C051F, "EXF", which is inverted when the command "EXX" is executed to transfer data between the main register

and the auxiliary register, is allocated to the first bit of memory address FFBFH.

P6FR (FFBFH

|                    | 7                                                   | 6                                                 | 5 | 4 | 3 | 2 | 1                                                       | 0            |

|--------------------|-----------------------------------------------------|---------------------------------------------------|---|---|---|---|---------------------------------------------------------|--------------|

| bit Symbol         | тозс                                                | TO1C                                              | _ | - | - | - | EXF                                                     | Fixed at "0" |

| Read/Write         | R /                                                 | w                                                 | - | - | - | - | R                                                       | -            |

| Resetting<br>value | 0                                                   | 0                                                 | - | - | - | - | Undefined                                               | 0            |

| Function           | 0: general<br>purpose<br>port<br>1: TO2/3<br>output | 0:general<br>purpose<br>port<br>1:TO0/1<br>output |   |   |   |   | EXX<br>instruction<br>Reverses<br>each time<br>executed | Write "0"    |

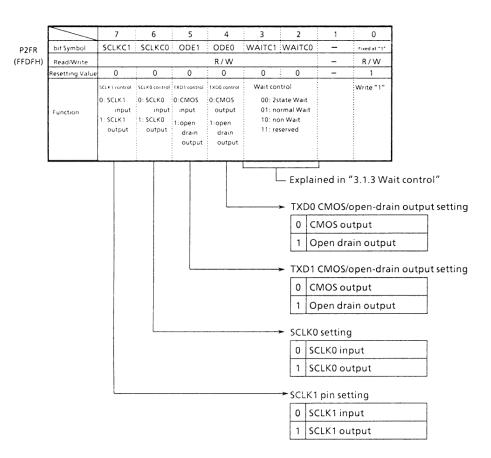

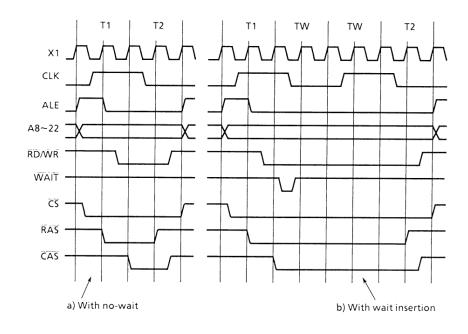

### 3.1.3 Wait Control

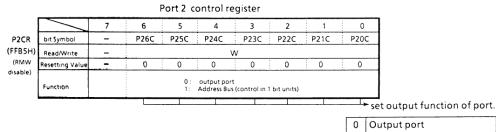

For TMP90C051F, a wait control register P2FR <WAITCO, 1> is

allocated to the 2th and 3th bits of memory address FFDFH.

P2FR (F

| FF | D | FI | Н | ) |

|----|---|----|---|---|

|                    | 7      | 6                                        | 5                                                                  | 4                                                                  | 3        | 2                                | 1 | 0            |

|--------------------|--------|------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|----------|----------------------------------|---|--------------|

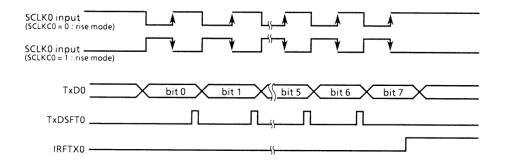

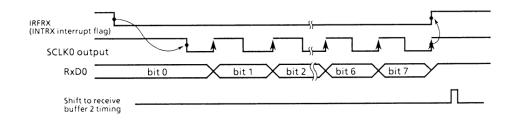

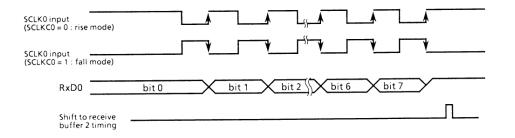

| bit Symbol         | SCLKC1 | SCLKC0                                   | ODE1                                                               | ODE0                                                               | WAITC1   | WAITC0                           | - | Fixed at "1" |

| Read/Write         |        |                                          | R / W                                                              |                                                                    | R /      | w .                              | - | R/W          |

| Resetting<br>Value | 0      | 0                                        | 0                                                                  | 0                                                                  | 0        | 0                                | - | 1            |

| Function           |        | CONTROL<br>0: SCLK0<br>input<br>1: SCLK0 | TXD1<br>CONTROL<br>0: CMOS<br>output<br>1: Open<br>drain<br>output | TXD0<br>CONTROL<br>0: CMOS<br>output<br>1: Open<br>drain<br>output | 00: 2 st | tate Wait<br>rmal Wait<br>n Wait |   | Write "0"    |

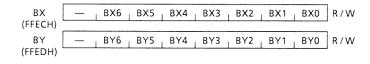

# 3.1.4 Bank Register

For TMP90C051F, BX and BY registers are allocated to memory addresses FFECH (BX register) FFEDH (BY register),

r

respectively. In these registers, only the low-order 7 bits are valid, and the high-order 1 bit are undefined. These undefined bits become "1" whenever they are read.

|               |                          | 7     | 6        | 5        | 4        | 3               | 2        | 1        | 0        |

|---------------|--------------------------|-------|----------|----------|----------|-----------------|----------|----------|----------|

| вх            | bit Symbol               | -     | BX6      | BX5      | BX4      | BX3             | BX2      | BX1      | BX0      |

| (FFECH)       | Read/Write               | -     |          |          |          | R / W           |          |          |          |

|               | Resetting<br>Value       | -     | 0        | 0        | 0        | 0               | 0        | 0        | 0        |

|               |                          |       |          |          |          |                 |          |          |          |

|               |                          |       | E .      |          |          |                 | 2        |          |          |

| RV            | bit Symbol               | 7     | 6<br>BY6 | 5<br>BY5 | 4<br>BY4 | 3<br>BY3        | 2<br>BY2 | 1<br>BY1 | 0<br>BY0 |

| BY<br>(FFEDH) | bit Symbol<br>Read/Write | 7<br> | 6<br>BY6 | 5<br>BY5 | 4<br>BY4 | 3<br>BY3<br>R/W | 2<br>BY2 | 1<br>BY1 | 0<br>BY0 |

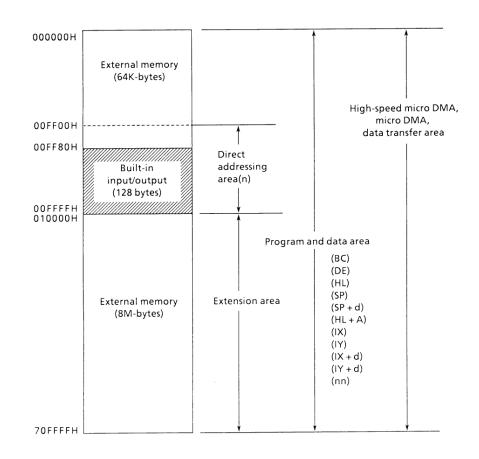

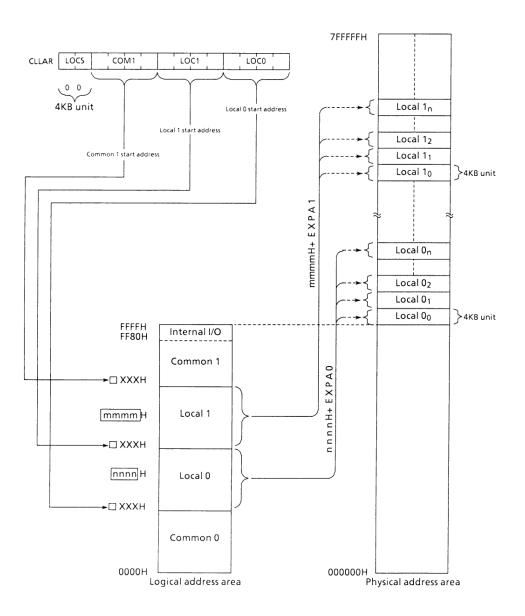

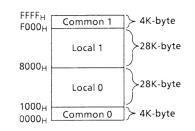

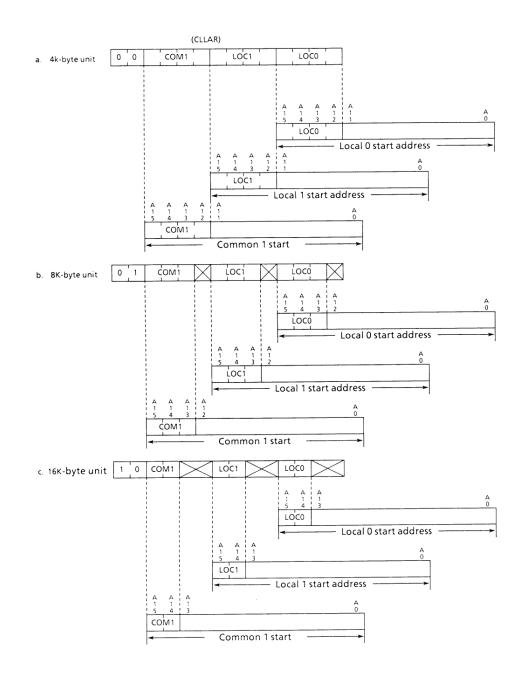

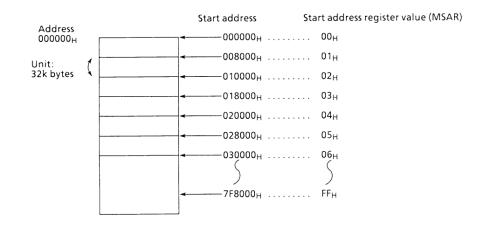

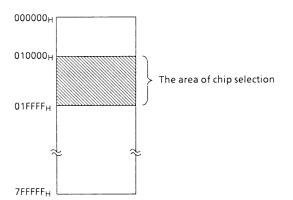

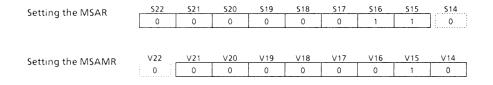

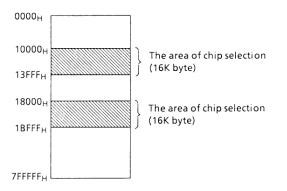

### 3.2 Memory Map

The TMP90C051F supports a program memory and a data memory of maximum 8M bytes.

The program and data memory may be assigned to the address space from 00000H to 7FFFFFH.

### 3.2.1 Internal I/O

The TMP90C051F provides a 128-byte address space as an internal I/O area, whose addresses range from FF80H to FFFFH. This I/O area can be accessed by the CPU using a short opcode in the "direct addressing mode".

Figure 3.2 (1) is a memory map indicating the areas accessible by the CPU in the respective addressing mode.

Figure 3.2 (1). Memory Map

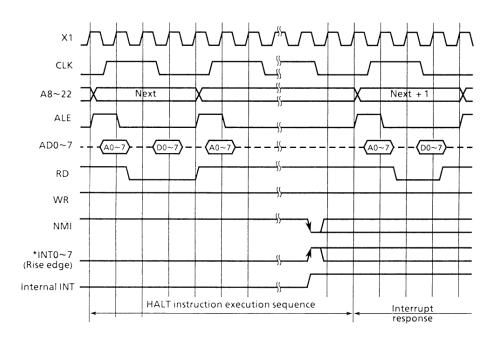

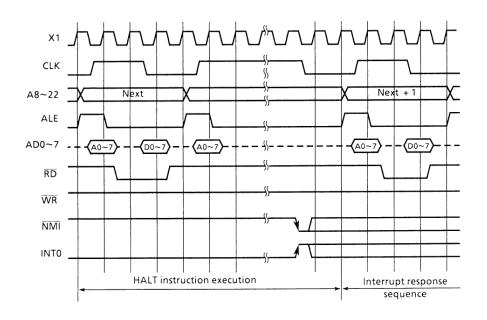

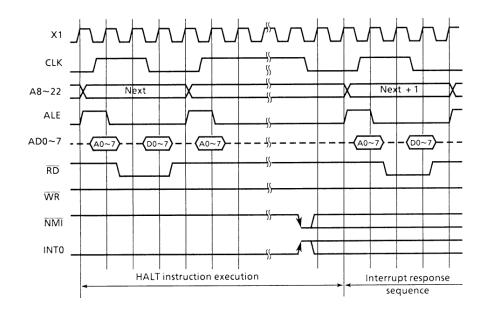

### **3.3 Interrupt Functions**

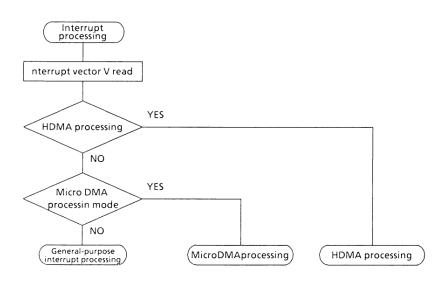

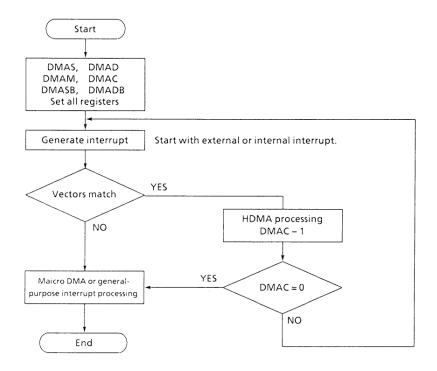

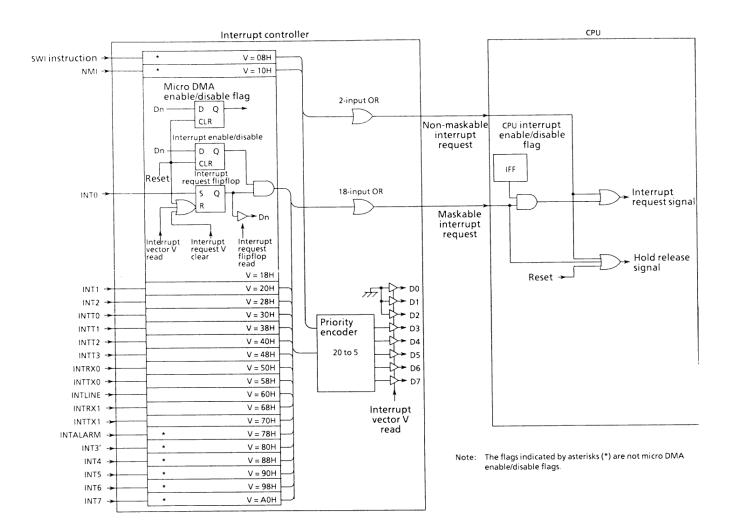

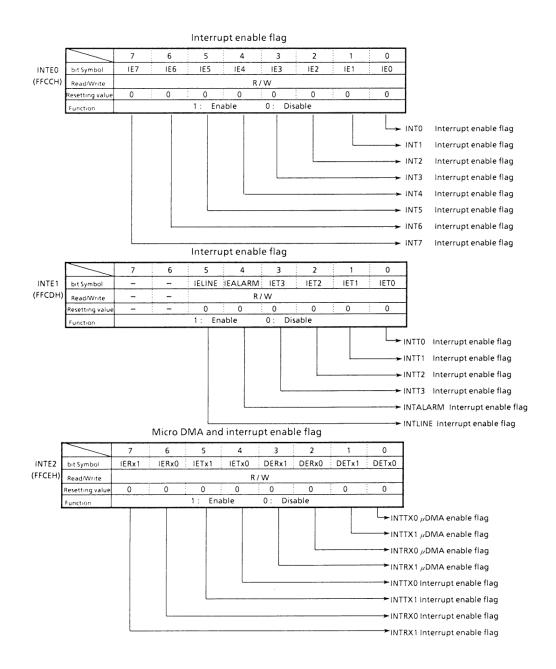

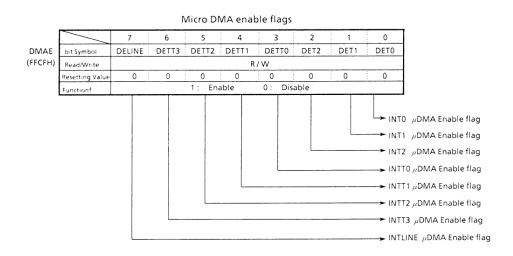

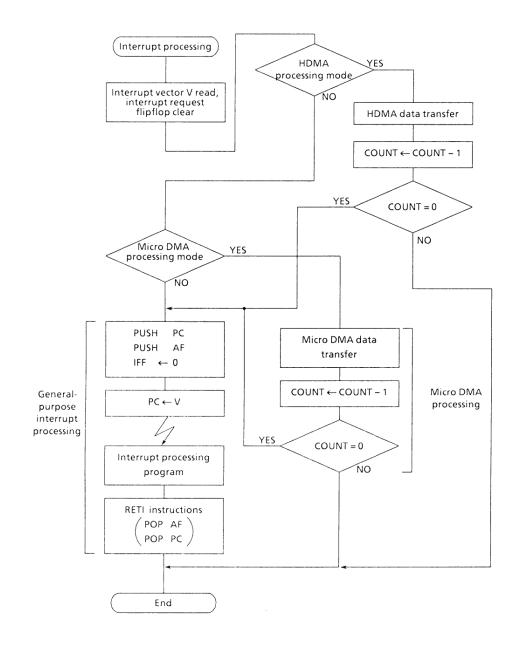

The TMP90C051F has a general-purpose interrupt processing routine for responding to both internal and external interrupt requests, a micro DMA processing mode in which the CPU automatically transfers data, and a high-speed micro DMA (HDMA) processing mode.

Immediately after a reset is released, all responses to

interrupt requests are set to the general-purpose interrupt processing mode. The interrupt requests can be set to the micro DMA processing mode with the DMA enable/disable register which is described later.

The high-speed DMA processing mode can be set by loading a vector value to the DMAV 0/1 register.

Figure 3.3 (1) shows the interrupt response flow.

Figure 3.3 (1). Interrupt Response Flow

When an interrupt request is generated, this is reported to the CPU via the built-in interrupt controller. If the request is for a non-maskable interrupt or an enabled maskable interrupt, the CPU starts interrupt processing. If for a disabled maskable interrupt, the request is ignored and not received.

If the interrupt is received, the CPU first reads the interrupt vector from the built-in interrupt controller to determine the source of the interrupt request.

Next, a check is made as to whether this request is for general-purpose interrupt processing, micro DMA processing or high-speed DMA (HDMA) processing, and then the corresponding processing is performed.

The interrupt vector is read in an internal operation cycle so the bus cycle becomes a dummy cycle.

#### 3.3.1 General-Purpose Interrupt Processing

Figure 3.3 (2) shows the general-purpose interrupt processing flow.

The CPU first saves the contents of the program counter PC and register AF (including the interrupt enable/disable flag IFF immediately before an interrupt) to the stack and then resets the interrupt enable/disable flag IFF to "0" (interrupt disable). Finally, the interrupt vector contents [V] are transferred to the program counter and a jump is made to the interrupt processing program.

There is a 20-state overhead from the time when the interrupt is received until the jump is made to the interrupt processing program.

Figure 3.3 (2). General-Purpose Interrupt Processing Flow

Interrupt processing program is ended with the RETI instruction for both maskable and non-maskable interrupts. Executing this instruction restores the program counter

PC and register AF contents from the stack. (Resets the interrupt enable/disable flag immediately before an interrupt.)

When the CPU reads the interrupt vector, the interrupt request source confirms that the interrupt has been received and then clears the interrupt request. Non-maskable interrupts cannot be disabled by program. Maskable interrupts, how-ever, can be enabled and disabled by program. Bit 5 of CPU reg-

ister F is an interrupt enable/disable flipflop (IFF). Interrupts are enabled by setting this bit to "1" with the El (interrupt enable) instruction and disabled by resetting this bit to "0" with the Dl (interrupt disable) instruction. IFF is reset to "0" by resetting and when an interrupt is received (including non-maskable interrupts).

The El instruction is actually executed after the next instruction is executed.

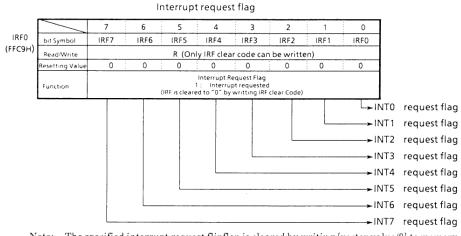

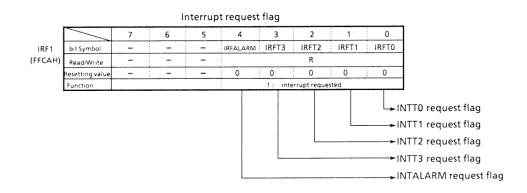

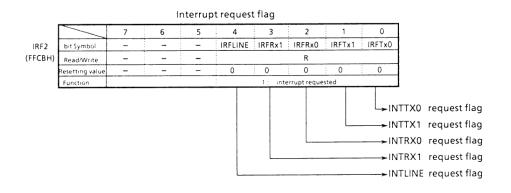

Table 3.3 (1) shows the interrupt sources.

|                      |          |                               |                              |                                                     | .,                      |                                          |                    |          |            |

|----------------------|----------|-------------------------------|------------------------------|-----------------------------------------------------|-------------------------|------------------------------------------|--------------------|----------|------------|

|                      |          | Intermed                      | Internut                     | General-                                            | R4: eve                 | Micro DMA                                | Interrupt sources  |          |            |

| Priority<br>sequence | Туре     | Interrupt<br>function<br>name | Interrupt<br>vector<br>value | purpose<br>interrupt<br>processing<br>start address | Micro<br>DMA<br>support | processing<br>parameter start<br>address | Internal           | External | Comments   |

| 1                    | Non-     | SWI                           | 08H                          | 0008H                                               | -                       | -                                        | 0                  | _        | -          |

| 2                    | maskable | Instruction<br>NMI            | 10H                          | 0010H                                               | _                       | _                                        | -                  | NMI pin  | _          |

| 3                    |          | (HDMA)                        | -                            | -                                                   | -                       | -                                        | _                  | -        | *1         |

| 4                    |          | INTO                          | 18H                          | 0018H                                               | 0                       | FF18H                                    | -                  | INTO pin | External 0 |

| 5                    |          | INT1                          | 20H                          | 0020H                                               | 0                       | FF20H                                    | -                  | INT1 pin | External 1 |

| 6                    |          | INT2                          | 28H                          | 0028H                                               | 0                       | FF28H                                    | -                  | INT2 pin | External 2 |

| 7                    |          | INTTO                         | 30H                          | 0030H                                               | 0                       | FF30H                                    | Timer 0            | -        | Timer      |

| 8                    |          | INTT1                         | 38H                          | 0038H                                               | 0                       | FF38H                                    | Timer 1            | -        | Timer      |

| 9                    |          | INTT2                         | 40H                          | 0040H                                               | 0                       | FF40H                                    | Timer 2            | -        | Timer      |

| 10                   |          | INTT3                         | 48H                          | 0048H                                               | 0                       | FF48H                                    | Timer 3            | -        | Timer      |

| 11                   |          | INTRX0                        | 50H                          | 0050H                                               | 0                       | FF50H                                    | Serial receive end | -        | SIO        |

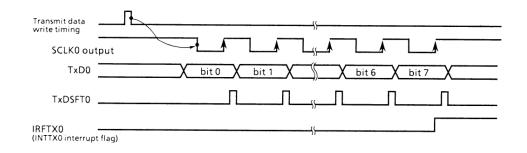

| 12                   | Maskable | INTTX0                        | 58H                          | 0058H                                               | 0                       | FF58H                                    | Serial send end    | -        | SIO        |

| 13                   |          | INTLINE                       | 60H                          | 0060H                                               | 0                       | FF60H                                    | TPH send           | -        | TPH        |

| 14                   |          | INTRX1                        | 68H                          | 0068H                                               | 0                       | FF68H                                    | Serial receive end | -        | SIO        |

| 15                   |          | INTTX1                        | 70H                          | 0070H                                               | 0                       | FF70H                                    | Serial receive end | -        | SIO        |

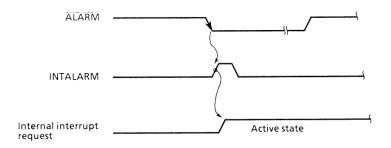

| 16                   |          | INTALARM                      | 78H                          | 0078H                                               | -                       | -                                        | Alarm output       | -        | RTC        |

| 17                   |          | INT3                          | 80H                          | 0080H                                               | -                       | -                                        | -                  | INT3 pin | External 3 |

| 18                   |          | INT4                          | 88H                          | 0088H                                               | -                       | -                                        | -                  | INT4 pin | External 4 |

| 19                   |          | INT5                          | 90H                          | 0090H                                               | -                       | -                                        | -                  | INT5 pin | External 5 |

| 20                   |          | INT6                          | 98H                          | 0098H                                               | -                       | -                                        | -                  | INT6 pin | External 6 |

| 21                   |          | INT7                          | A0H                          | 00A0H                                               | -                       | -                                        | -                  | INT7 pin | External 7 |

Table 3.3 (1) Interrupt Sources

Note: \* HDMA supports all maskable interrupts.

The "priority sequence" shown in Table 3.3 (1) indicates the sequence in which interrupt sources are received by the CPU when multiple interrupt requests are generated simultaneously.

For example, if interrupt requests with the priority sequences 4 and 5 are generated simultaneously, the CPU will receive the interrupt request with priority sequence 4 first. When processing of the interrupt with priority sequence 4 is ended with the RETI instruction, the CPU will then receive the interrupt with priority sequence 5.

If the interrupt processing program for the priority sequence 4 interrupt is interrupted by executing the El instruction, the CPU will receive the priority sequence 5 interrupt request. When multiple interrupt requests are generated simultaneously, the built-in interrupt controller only determines the priority sequence of the interrupt sources received by the CPU. There is no function to compare the priority sequence of the interrupt currently being processed and the interrupt currently being requested.

Another interrupt can be enabled while another interrupt is being processed by resetting the interrupt enable/disable flag IFF to enable.

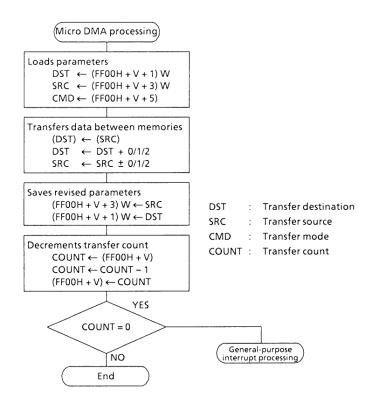

## 3.3.2 Micro DMA Processing

Figure 3.3 (3) shows the micro DMA processing flow. The CPU first loads the parameters (transfer source and destination addresses, transfer mode) required for transferring data between memories from the address modified by the interrupt vector value and then transfers the data between memories in accordance with those parameters. After that, the revised parameters are saved to the original location. The transfer count is then decremented and, if the value is not "0", micro DMA processing is ended. If the value is "0", the general-purpose interrupt processing described in the previous item is performed.

The transfer count is decremented by "-1" each time the micro DMA starts up.

Figure 3.3 (3). Micro DMA Processing Flow

Since most interrupt processing involves only simple data transfers, micro DMA processing uses only the hardware for such processing. Consequently, micro DMA processing is faster than conventional software processing. Naturally, there is absolutely no influence on the CPU registers from the micro DMA processing.

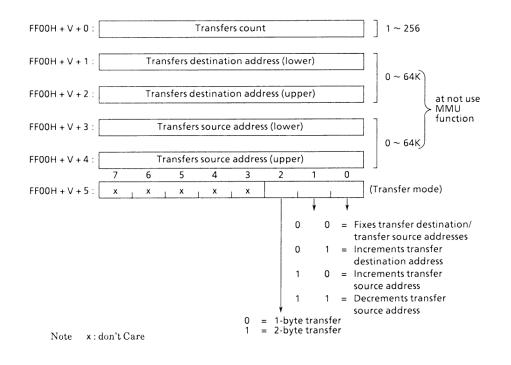

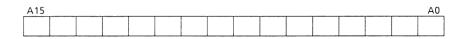

Figure 3.3 (4) shows the functions of the parameters used in the micro DMA processing.

Figure 3.3 (4). Micro DMA Processing Parameters

The parameters used for the micro DMA processing are located in the external RAM area (See Table 3.3 (1) Interrupt sources). The start address of each micro DMA processing parameter is [FF00H + interrupt vector value], 6 bytes of which are used for the parameters. When the micro DMA processing mode is not used, this area can be used as user memory.

The parameters include transfer count, transfer destination address, transfer source address and transfer mode. Transfer count specifies the number of times data will be transferred by micro DMA processing. Either 1 or 2- bytes of data are transferred at one time by micro DMA processing. Data are transferred 256 times with a transfer count of "00H".

The addresses 0000H - FFFFH are used in micro DMA processing (at not use MMU function). Bits 0 and 1 specify the transfer destination or transfer source address change mode. Bit 2 specifies the length (1 or 2 bytes) of the data handled.

Table 3.3 (2) shows the relationship between the transfer mode and transfer destination/transfer source address increment/decrement values.

| Transfer<br>Mode | Function                                                           | Transfer destination<br>address | Transfer source<br>address |

|------------------|--------------------------------------------------------------------|---------------------------------|----------------------------|

| 000              | Transfers 1-byte, fixes transfer destination/source addresses.     | 0                               | 0                          |

| 001              | Transfers 1-byte, increment s transfer destination address.        | +1                              | 0                          |

| 010              | Transfers 1-byte, increment transfer source address.               | 0                               | +1                         |

| 011              | Transfers 1-byte, decrement transfer source address.               | 0                               | -1                         |

| 100              | Transfers 2-bytes, fixes the current destination/source addresses. | 0                               | 0                          |

| 101              | Transfers 2-bytes , increment transfer destination address.        | +2                              | 0                          |

| 110              | Transfers 2-bytes, increment transfer source address.              | 0                               | +2                         |

| 111              | Transfers 2-bytes, decrements, transfer source address.            | 0                               | -2                         |

#### Table 3.3 (2) Micro DMA Processing Address Changes

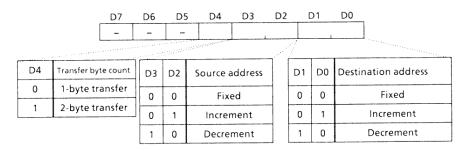

Data are transferred as shown below in the 2-byte transfer mode.

(Transfer source address)←(Transfer destination address) (Transfer source address + 1)←(Transfer destination address + 1)

Transfers are also performed as shown above in "decrement transfer source address mode" but address changes are as shown in Table 3.3.

Address incrementation and decrementation are used for

the memory area but fixed addresses are used for ordinary input/ output addresses. Because of that, micro DMA was designed taking into consideration input/output to memory and memory to input/output transfers.

Figure 3.3 (5) shows and example using the micro DMA processing mode. Built-in serial input/output receive data are processed in the example.

In the example, 7 frames (1 frame = 1 byte in this example) of received data are stored to memory address FF00H - FF06H and when all of the data have been received, the "receive end processing program" is executed.

| SET     | 6,(0FFCEH)            | ;     | Sets serial receive interrupt to micro DMA processing mode                         |

|---------|-----------------------|-------|------------------------------------------------------------------------------------|

| LD      | (OFF50H),7            | ;     | Sets transfer count to 7                                                           |

| LDW     | (OFF51H),OFF00H       | ;     | Sets transfer destination start address to FF00H                                   |

| LDW     | (OFF53H),OFFD2H       | ;     | Sets transfer source (serial receive buffer)<br>address to FFEBH                   |

| LD      | (FF55H),1             | ;     | Sets transfer mode ( transfers 1 byte,<br>increments transfer destination address) |

| EI      |                       |       |                                                                                    |

| :       |                       |       |                                                                                    |

| :       |                       |       |                                                                                    |

| ORG     | 0050H                 |       |                                                                                    |

| Receive | end interrupt process | ing p | program                                                                            |

RETI

Figure 3.3 (5). Micro DMA Processing Example

"Table 3.2 Bus operations for each instruction" above shows the bus operation for general-purpose interrupt processing and micro DMA processing.

The execution time (when the transfer count is not 0 after

decrementation) for micro DMA processing is 46 states (9.2 microseconds at 10MHz), regardless of whether the 1-byte or 2-byte transfer mode is used.

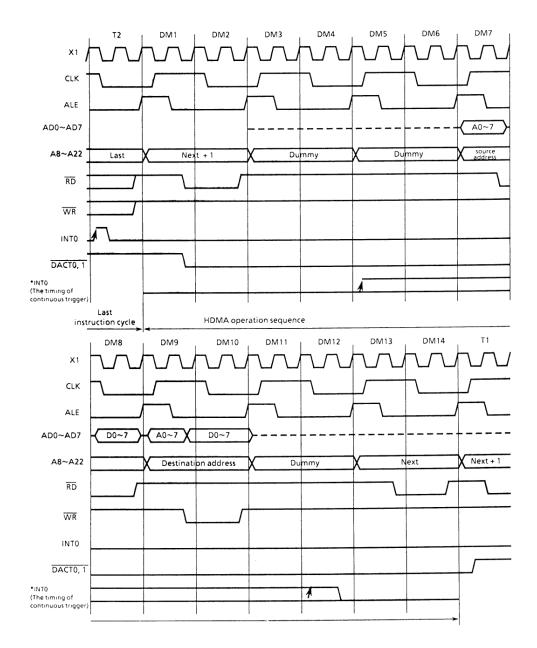

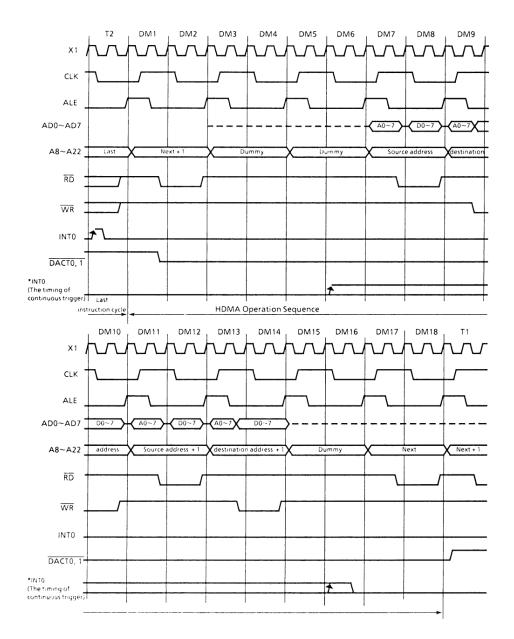

### 3.3.3 High-Speed Micro DMA Processing

The TMP90C051F has two built-in DMA channels called HDMA.

HDMA has three times the processing capacity of  $\mu$ DMA and is used for high-speed data transfers. HDMA execution

time (decrease the value of transfer number and the value is not "0" data) is 14 states, regardless of whether the 1-byte transfer mode or 2-byte transfer mode is used. HDMA and micro DMA transfer speeds.

Table 3.3 (3) shows the high-speed micro.

| fxtal (MHz) | HDMA   | Micro DMA |

|-------------|--------|-----------|

| 10          | 2.8µs  | 9.2µs     |

| 12.5        | 2.24µs | 7.36µs    |

| 16          | 1.75µs | 5.75µs    |

#### Table 3.3 (3) Transfer Speeds

\* At 1-byte transfer mode.

| Number of channels    | 2                                                          |

|-----------------------|------------------------------------------------------------|

| Transfer speed        | 14 states (for 1 byte) or 18 states (for 2 bytes)          |

| Start method          | By interrupt (all external and internal interrupt sources) |

| Transfer mode         | 1 byte transfer or 2 byte transfer                         |

| Address output method | Dual address (source/destination)                          |

| Access area           | 0 ~ 8-M byte memory area (64k-byte units)                  |

#### Table 3.3 (4) Shows the HDMA function

(1) HDMA Setting Registers

HDMA operation.

The following describes the registers required for

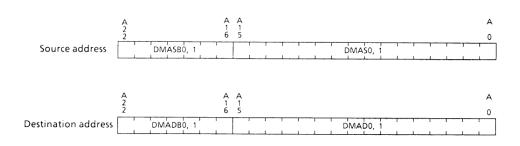

(a) DMASO, 1: source address register (16-bit)

(b) DMA0, 1: Destination address register (16-bit)

(c) DMAC0, 1: byte count register (16-bit)

Sets the number of bytes to be transferred. The set value is decremented (-1) for each HDMA started. A generation purpose interrupt is when the value reaches "0".

(d) DMAM0, 1: transfer mode register (8-bit)

This register determines the HDMA transfer mode. The bits of this register are as shown in the table above.

The source and destination addresses shown here are the addresses loaded to DMAS0, 1 and DMAD0, 1 above. Example 1 : XXX00001 Transfers 1 byte, fixes transfer source address (DMAS0, 1), and increments the transfer destination address after each

Example 2: The renewal of address at 2 byte transfer mode.

transfer.

Note: It is ineffective to set decrement for a destination address when a source address being increment; and to set increment for a destination address when a source address being decrement.

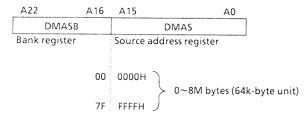

(e) DMASB0, 1: source address bank register

|                |                    | 7          | 6          | 5     | 4          | 3     | 2     | 1          | 0     |

|----------------|--------------------|------------|------------|-------|------------|-------|-------|------------|-------|

| DMASB0         | bit Symbol         | -          | DSB06      | DSB05 | DSB04      | DSB03 | DSB02 | DSB01      | DSB00 |

| FFF6H)         | Read/Write         | -          |            |       |            | R/W   |       |            |       |

|                | Resetting<br>Value | _          | 0          | 0     | 0          | 0     | 0     | 0          | 0     |

|                | value              |            |            |       |            |       |       |            |       |

|                | Value              | 7          | 6          | 5     | 4          | 3     | 2     | 1          | 0     |

|                | bit Symbol         | 7          | 6<br>DSB16 |       | 4<br>DSB14 | ·     |       | 1<br>DSB11 | 0     |

| MASB1<br>FF9H) |                    | 7<br><br>- |            | 5     |            | 3     | 2     | 1          |       |

Source address extension register Used as a pair with the DMAS0, 1 register, this bank register is specified for addresses for 64k bytes or more.

This register has no increment or decrement function; therefore, it is necessary to exercise caution in specifying variable addresses (increment or decrement) with the above mode register.

(f) DMADB0, 1: destination address bank register

|                   |                          | 7     | 6          | 5          | 4          | 3                 | 2          | 1          | 0          |

|-------------------|--------------------------|-------|------------|------------|------------|-------------------|------------|------------|------------|

| DMAD80            | bit Symbol               | -     | DDB06      | DDB05      | DDB04      | DDB03             | DDB02      | DDB01      | DDB00      |

| (FFF7H)           | Read/Write               | -     |            |            |            | R/W               |            |            |            |

|                   | Resetting<br>Value       |       | 0          | 0          | 0          | 0                 | 0          | 0          | 0          |

|                   |                          |       |            |            |            |                   |            |            |            |

|                   |                          |       |            |            |            |                   |            |            |            |

|                   |                          | 7     | 6          | 5          | 4          | 3                 | 2          | 1          | 0          |

| DMADB1            | bit Symbol               | 7     | 6<br>DDB16 | 5<br>DDB15 | 4<br>DDB14 | 3<br>DDB13        | 2<br>DDB12 | 1<br>DDB11 | 0<br>DDB10 |

| DMADB1<br>(FFFAH) | bit Symbol<br>Read/Write | 7<br> |            | 5<br>DDB15 | 4<br>DDB14 | 3<br>DDB13<br>R/W | 2<br>DDB12 | 1<br>DDB11 | 0<br>DDB10 |

Destination address register Used as a pair with the DMAD0, 1 register. The function are the same as those of the DMASB0/1.

(g) DMAV0, 1: DMA vector register

|                   |                    | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

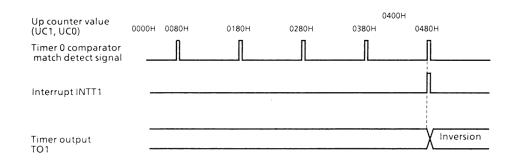

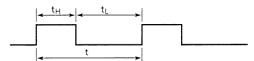

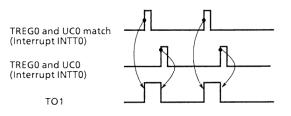

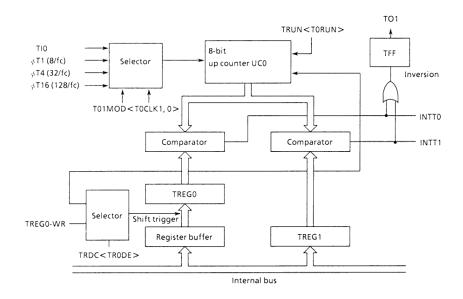

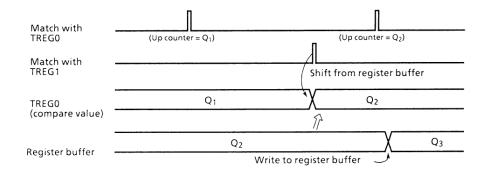

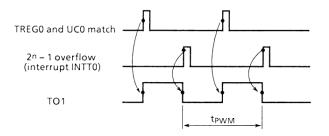

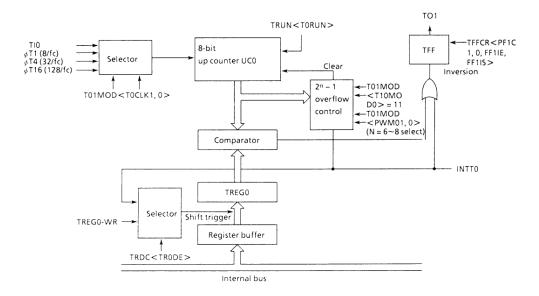

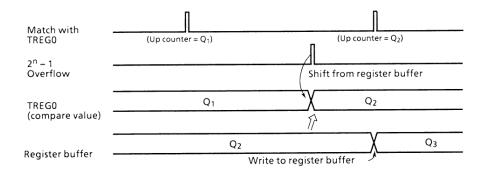

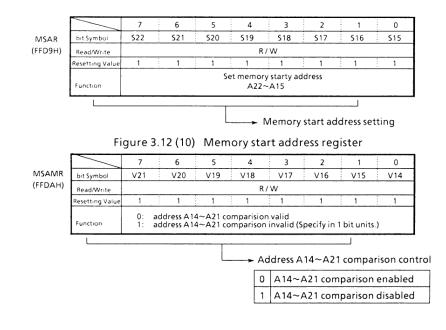

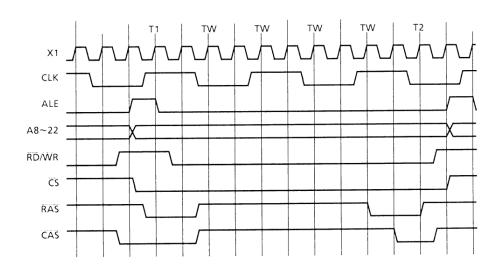

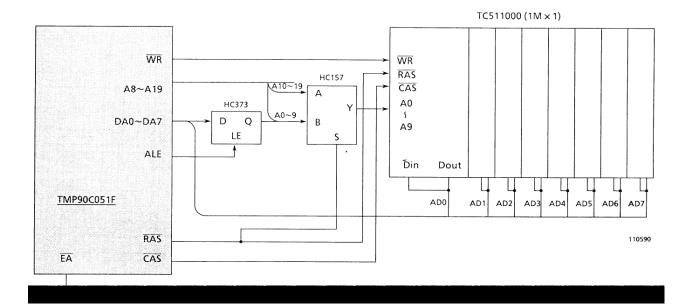

|-------------------|--------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|